采用risc-v架构的处理器不经意出现在日常电子产品中,似乎已经变得越来越稀松平常了:不仅是一些典型的mcu厂商开始拥抱risc-v。

而且还体现在一些业已成熟的产品中,如今年的中国ic领袖峰会上,,了解到如今十分成熟的tcon芯片内部竟也不显山、不露水地加入了risc-v小核心;还有像是前些年英伟达就开始在其gpu产品中选择risc-v作为控制器;西数也在整个产品线上开始选择risc-v核。

这让我们对于risc-v指令集的处理器微架构也愈发感兴趣:去年10月,sifive发布了首款risc-v乱序cpu核心,u8系列处理器ip。sifive在宣传中提到,u8系列是目前最高性能的risc-v指令集核心ip(似乎晚于玄铁910),“基于超标量乱序管线,以及可配置的管线深度和发射序列宽度”。

sifive在risc-v的微架构ip授权中还是相当活跃的一家企业,其7系与8系ip核,作为risc-v世界的高性能核心,是我们观察risc-v当前发展情况的一个重要窗口,虽然微架构剖析大约并不能特别好地呈现指令集本身的特性,但通过它们与arm的对比,也是了解risc-v生态的机会。

最高性能的risc-v核心,比起arm如何?

我们首先有必要搞清楚,sifive内部针对不同系列的产品的定位。在今年4月sifive举行的一场名为"embedding intelligence everywhere with sifive 7 series core ip"的在线会议上,sifive曾经对自家产品线进行过总结。sifive的e系列核心,着眼在32bit嵌入式使用场景;64bit的s核心则偏向算力需求更大的场景;而u系列核心是性能最强的定位,面向高端计算。

若以数字为切分维度,sifive的2系列是risc-v处理器ip中效率最高,同时也最小型的处理器ip;3系列、5系列则在部署上更为广泛,用在一些多核配置和对实时处理能力要求较高的场景;7系列和8系列如上所述都着力于高性能。数字与字母组合,就构成了不同的产品,比如说e3面向中端定位的嵌入式应用提供32bit性能;s7显然是专注在性能方面的产品;u8则实现了可规模化配置的高性能核心,达成最高的每瓦性能。

在u8发布之前,sifive的高算力产品主要就是u5、u7——这两者仍是顺序架构,对标的是arm的低端及微控制器核心,在面对更为复杂的负载、要求算力的场景下还是有欠缺的。u8系列是弥补这个短板的产品。sifive当时宣称,u8将极大扩展sifive与risc-v在终端产品中的生态系统生存能力。

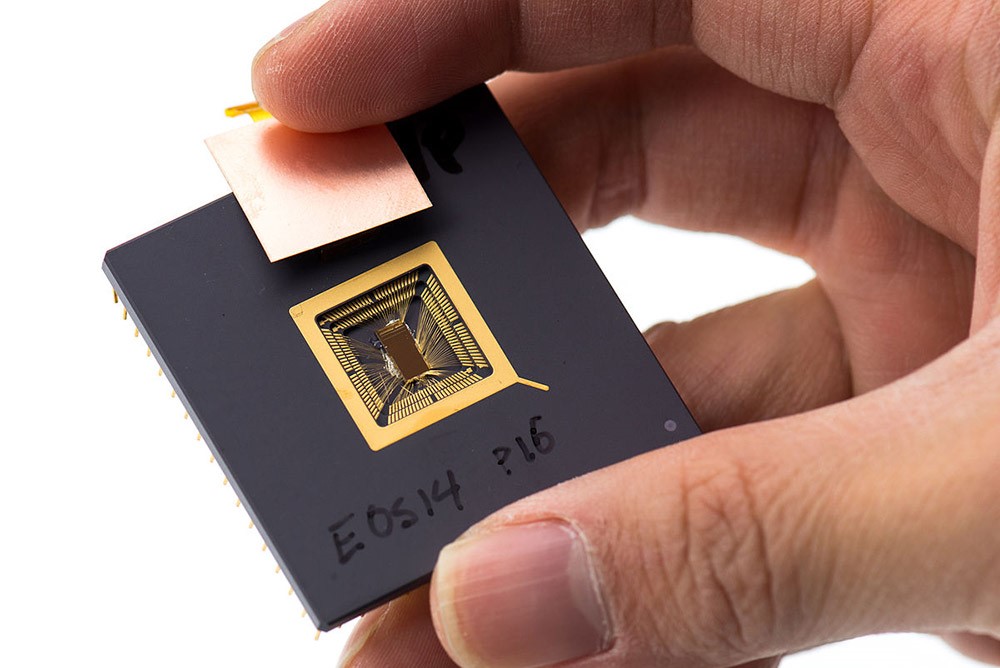

在sifive u8系列产品下,目前主要包括u84、u87两个核心ip。sifive自己给的数据是,u84核心的性能是u74的3.1倍,ipc提升2.3倍(在最高频率提升1.4倍的情况下)。上面这张图对比中,在相同工艺的前提下,u84性能是u54的5.3倍;如果加上工艺造成的差别,则7nm的u84核心,性能达到了28nm的u54核心的7.2倍。这个数据其实一方面表明,risc-v的性能潜力这些年还在挖掘过程中,所以相比更低端的产品能有如此巨量的性能与效率差距。

这是risc-v自己内部在fpga平台下跑u84 ip的成绩,比较的是specint2006成绩。

sifive此前在新闻稿中给u8树立的直接竞争对手是arm cortex-a72,其中提及相比arm cortex-a72核心,sifive u84提供可媲美的性能。不过在面积效益和每瓦性能方面,u84还是有优势,当然我们知道a72已经是arm前两年的架构了。

同是7nm工艺的前提下,u84的每个核心占地面积在0.28mm²,四个核心加上2mb l2 cache构成一个簇,面积为2.63mm²。此前华为krin 980的cortex-a55小核心,每个核心配上各自128kb的l2 cache,面积为0.36mm²——要知道a72的性能是a55的两倍还多,显然在ppa方面,sifive u84表现不错。

需要强调的是,u8系列作为ip在面向具体的芯片产品时还是有很大的可配置和扩展性的,u84是作为一个标准ip存在的,所以这里的探讨仅基于sifive的标准ip,具体到实际产品仍然会有差别。

7系列与8系列微架构

或许很多人并不会将risc-v这样一个指令集,在高性能领域去与arm一决高下,毕竟risc-v当前的主场也不在此——iot产品对碎片化问题更不敏感,也不像手机那样对处理器性能有那么高的要求,risc-v在很多情况下也偏向以微控制器的姿态存在。不过在我们看来,这依然是表现risc-v阵营技术能力的重要组成部分。

risc-v可查阅的资料当然还远没有arm世界那么多,已经商用的risc-v处理器——无论是mcu中的处理器,还是某些硬件中的控制器,公开的技术细节也并不多,详实程度自然不及遍地开花的arm。我们从有限的资料中去了解sifive的7系列与8系列处理器微架构,对于理解risc-v生态还是有价值的。

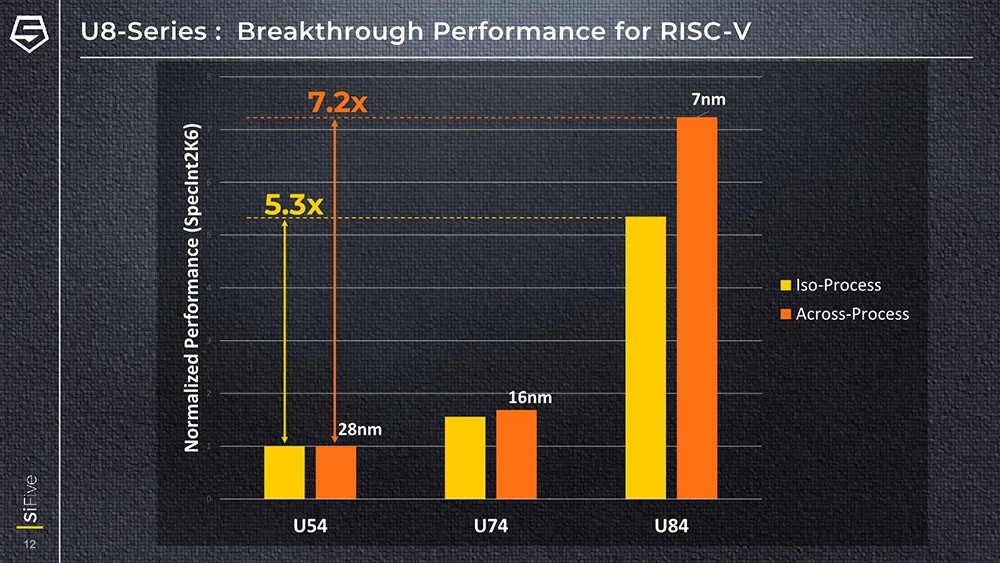

如前文所述,u8系列是sifive的首款乱序核心,u84流水线深度12级,后端3个执行单元——还是相当传统的乱序执行设计。这里的寄存器组(regfile)设计还是颇为与众不同。

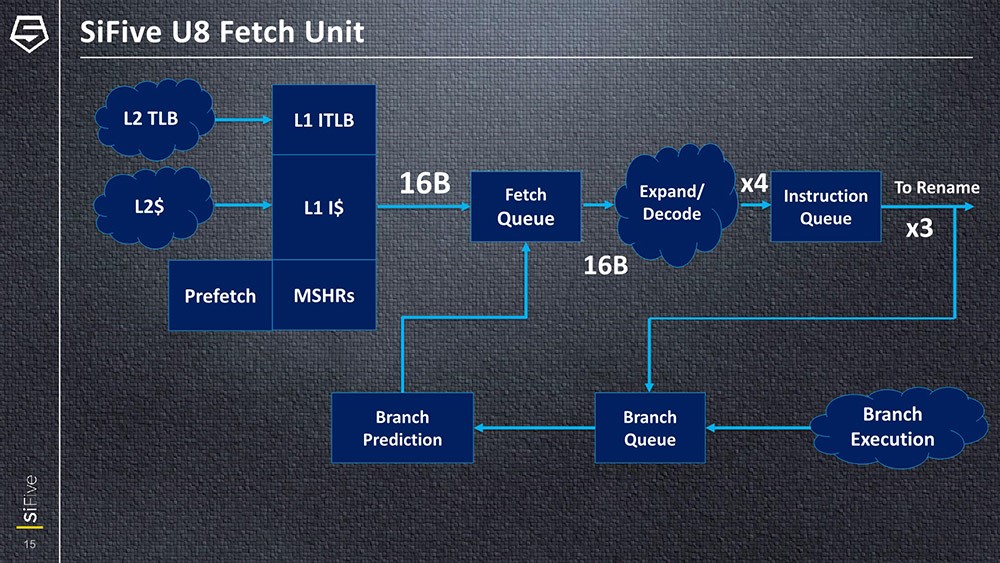

从前端来看,核心的取指单元(fetch queue)能够每周期以16字节从l1l获取指令,将其放到取指队列中。risc-v isa为可变指令编码长度,假定平均是32bit,则对应每周期4个指令。所以u8的解码器(decoder)也是4-wide设计,并将其传递到指令队列(instruction queue)中。

再往后,指令队列能够一次发射3个指令到重命名阶段(rename),这个宽度就比前面收窄了。外媒anandtech此前也在针对这部分的评价中提到,取指阶段的宽度大于发射这种设计,旨在发生分支预测错误时,让前端能够跟上后端;但解码比发射更宽的这种设计,以前还从未见过。猜测这可能是微架构的某种平衡之策,也可能是为将来更宽发射的u8系列ip设计做准备的。从sifive的官方介绍来看,发射队列数应该是可以由芯片设计商来配置扩展的。

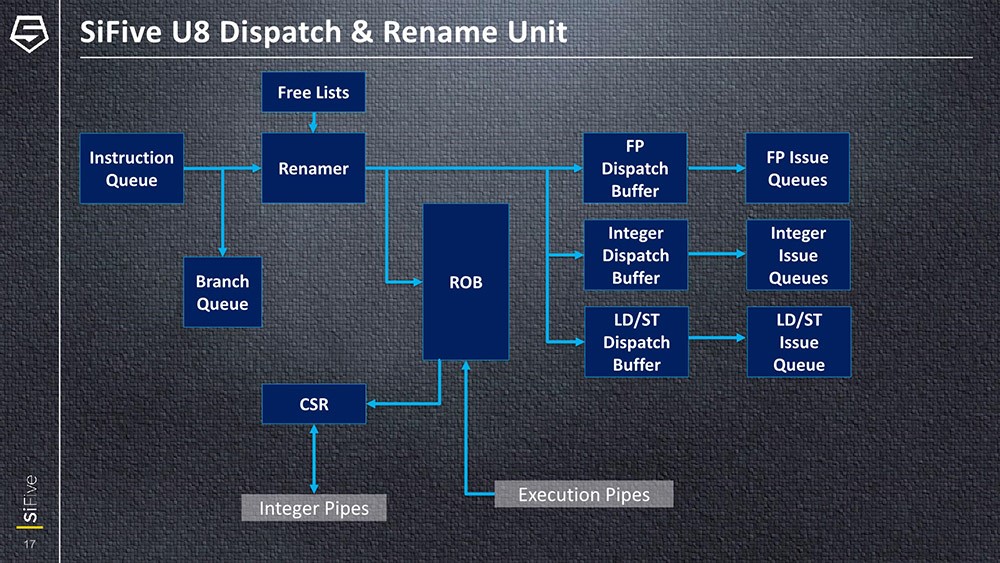

重命名阶段的设计比较常规,包含一个重排序buffer,和三个分发引擎。然后就进入到执行后端了。

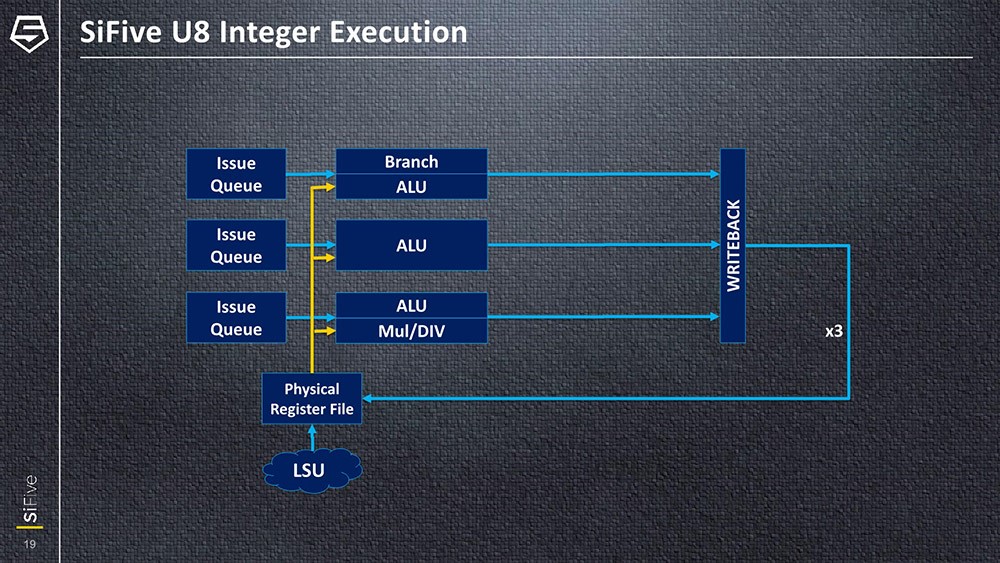

后端部分,sifive只给了整数执行单元的情况,整体包含3条执行管线。每一条都有其各自的发射队列,填充进3条alu管线。其中一条管线是常规的alu,有一条则与分支单元共享了端口,还有一条更为复杂,可以执行整数乘法和除法操作。

u84这样的核心本身还没有simd、矢量指令支持,似乎是因为扩展指令还未完全就绪。sifive解释说,今年年底这部分会就绪;可能u87就会具备这部分能力——目前我们从sifiveamjs澳金沙门线路首页官网还未看到这方面的更新。

可扩展性

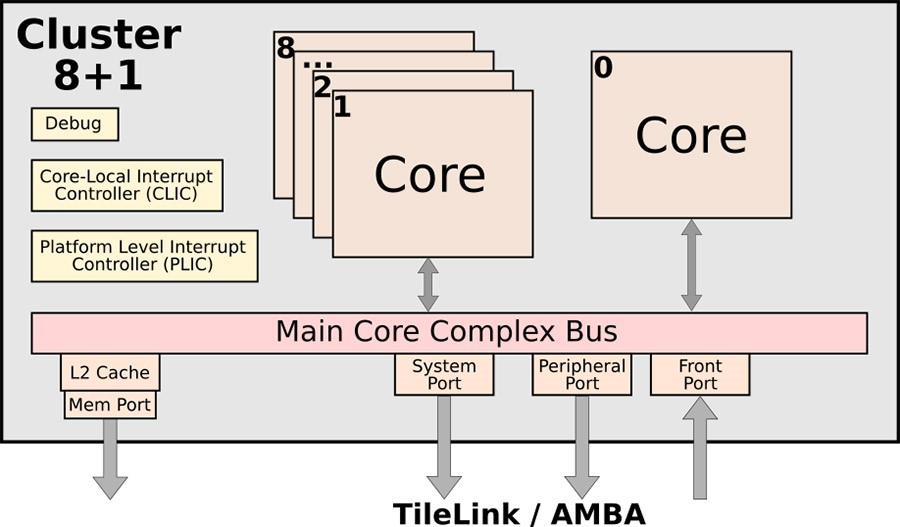

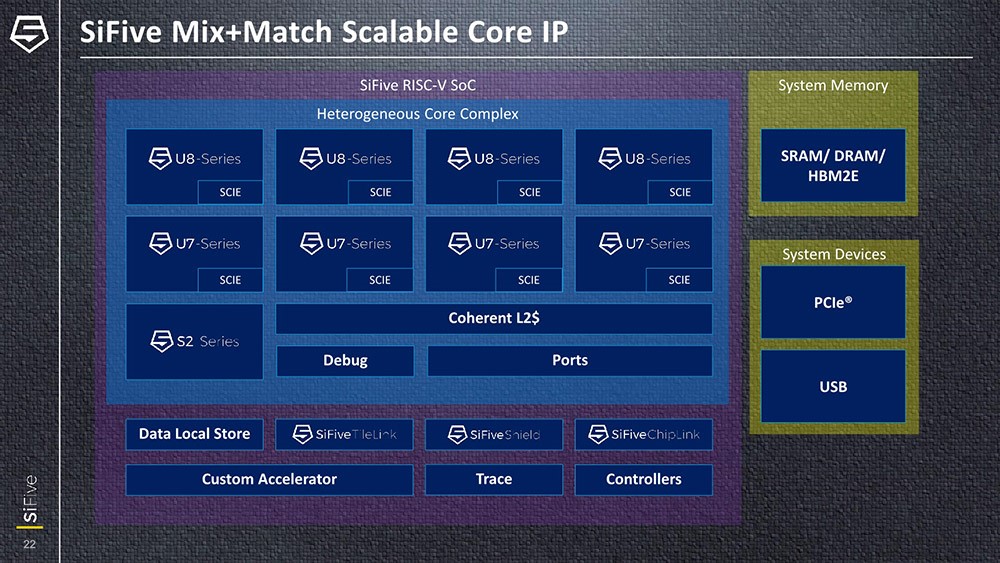

从构成soc/mcu的更高层级来说,sifive采用一种名为"mix match"的大小核异构设计,共享一个l2可以配置至多9个核心。核心的搭配方式,可以是u8、u7、s2这些不同的核心搭配组合。

参考早前的7系列,采用的是8 1设计,看起来和这次的设计比较相似,但搭配方式上可能会有些差别。wikichip所做的这张图更清晰地表达了这种结构——包括核心、cache等,整体构成一个簇(cluster)。其上还有自定义指令支持(custom instruction extensions),每个核心都能实现特定指令的支持,实现某些特定工作负载的加速——这也是现在很多基于risc-v指令微架构的能力。

7系列的介绍中曾提到,通过tilelink,可以将64个这样的簇放在一颗单芯片上。u8系列核心ip介绍中则只提到了使用tilelink,来连接第三方加速器ip实现core-to-core通信,或者chiplink实现chip-to-chip通信。存储子系统部分详情不多,sifive提到提供高带宽存储接口ip,对于hbm2e 这类需求有帮助,不过这部分工作似乎还在持续。

7系列的核心有可选配一种fio端口(fast i/o),直连到核心,作为核心以及大容量sram或第三方加速器之间的低延迟接口——这种fio端口还与main core complex bus总线相连,其他核心也能看到sram或者第三方加速器。不知道这种fio端口,与sifive的tilelink技术是什么样的关系。

在可扩展性的问题上,u8系列还有一些特性:(1)对不同工艺节点的支持;(2)乱序设计可做配置,前文提到u84这种标准核心是12级流水线、3发射,实际上流水线深度、发射队列数等都是可以针对不同应用做具体调整的;(3)整数单元到浮点单元的跨发射(cross-issue)能力;(4)“可组合cache”达成实时操作支持。

如前文所述,sifive的7系列与8系列在当今risc-v生态中可能没有充足的代表性,不过如sifive所言,这些高性能核心ip对于扩展risc-v生态边界还是有相当价值的。即便就现在看来,arm生态在中高端市场仍然占据着性能和技术上相当的优势。